C101Aは、初段FETに対する過電圧保護回路を備えています。そのため検出器へのバイアス電圧をオンオフするときに、バイアス電圧の時間変化にそれほど気をつかう必要はありません(ただし電圧限度(= ±500 V)は超えないよう注意は必要です)。

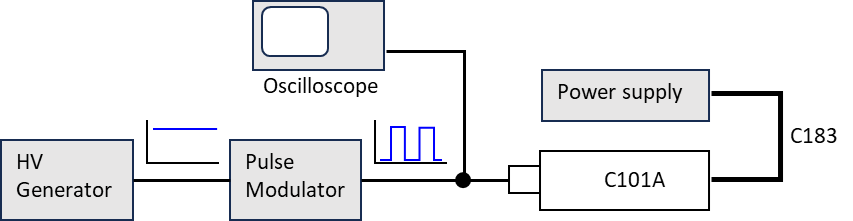

このことを示すため、図1の回路を用いて高電圧印加試験を実施しました。

図1 試験回路

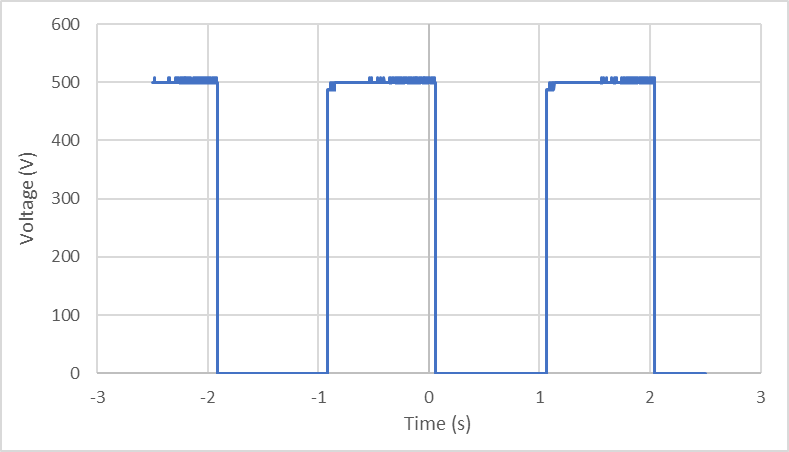

高電圧は、C101Aの入力コネクタ電極へ直接印加しました。通常の測定では高電圧電源と入力コネクタとの間に検出器が入りますが、厳しい条件とするために直結としています。C101Aのバイアス電源入力を使用せず入力コネクタ電極からの入力としたのも同様の理由です。実際の電圧波形を図2に示します。

図2 電圧波形(Oscilloscopeの波形)

なお、図2の電圧波形の立上がり時間(10% から 90%)は 1 ms、立下り時間(90% から 10%)は 0.5 msとなっています。

図2に示したように、+500 V と 0 Vとを1秒間隔で切り替えて、電圧を1000回(所要時間:約2000秒)スイッチングしました。その間にC101Aの電源はオンした状態(= ±12 Vを供給している状態)としています。

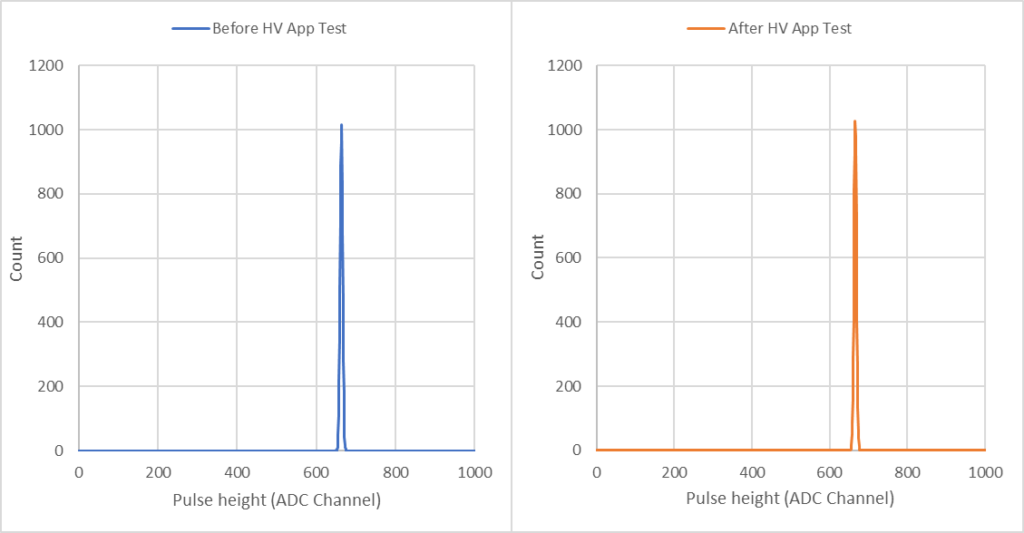

この試験を実施した後、C101Aに故障等は全く見られませんでした。試験実施前と実施後とのテストパルスのスペクトルを図3(a)に示します。性能も変化していないことがわかります。

(a) 試験実施前 (b) 試験実施後

図3 試験実施前後におけるテストパルスのスペクトル

なお、C102AもC101Aと同一の回路を使用しており、C102に対しても同様です。